# integration with integrity

User's Manual Mini-ITX Motherboard 2807780 Version 1.0

# Copyrights

This manual is copyrighted and all rights are reserved. It does not allow any non authorization in copied, photocopied, translated or reproduced to any electronic or machine readable form in whole or in part without prior written consent from the manufacturer.

In general, the manufacturer will not be liable for any direct, indirect, special, incidental or consequential damages arising from the use of inability to use the product or documentation, even if advised of the possibility of such damages. The manufacturer keeps the rights in the subject to change the contents of this manual without prior notices in order to improve the function design, performance, quality and reliability. The author assumes no responsibility for any errors or omissions, which may appear in this manual, nor does it make a commitment to update the information contained herein.

# **Trademarks**

Intel is a registered trademark of Intel Corporation.

Award is a registered trademark of Award Software, Inc.

All other trademarks, products and or product's name mentioned herein are mentioned for identification purposes only, and may be trademarks and/or registered trademarks of their respective companies or owners.

#### Safety Instructions

- Always read the safety instructions carefully.

- Keep this User's Manual for future reference.

- 3. Keep this equipment away from humidity.

- 4. Lay this equipment on a reliable flat surface before setting it up.

- The openings on the enclosure are for air convection hence protects the equipment from overheating. DO NOT COVER THE OPENINGS.

- Make sure the voltage of the power source and adjust properly 110/220V before connecting the equipment to the power inlet.

- Place the power cord such a way that people can not step on it. Do not place anything over the power cord.

- 8. Always Unplug the Power Cord before inserting any add-on card or module.

- 9. All cautions and warnings on the equipment should be noted.

- Never pour any liquid into the opening that could damage or cause electrical shock.

- 11. If any of the following situations arises, get the equipment checked by service personnel:

- † The power cord or plug is damaged.

- † Liquid has penetrated into the equipment.

- † The equipment has been exposed to moisture.

- † The equipment does not work well or you can not get it work according to User's Manual

- † The equipment has dropped and damaged.

- † The equipment has obvious sign of breakage.

- 12. DO NOT LEAVE THIS EQUIPMENT IN AN ENVIRONMENT UNCONDITIONED, STORAGE TEMPERATURE ABOVE 60°C (140°F), IT MAY DAMAGE THE EQUIPMENT.

**CAUTION:** Danger of explosion if battery is incorrectly replaced. Replace only with the same or equivalent type recommended by the manufacturer.

·這是甲數的資訊產品,在居住的環境中使用時,可能會造成無線電干擾, 在這種情況下,使用者會被要求採取某些適當的對策。

廢電池請回收

For better environmental protection, waste batteries should be collected separately for recycling or special disposal.

#### FCC-B Radio Frequency Interference Statement

This equipment has been tested and found to comply with the limits for a Class B digital device, pursuant to Part

15 of the FCC Rules. These limits are designed to provide reasonable protection against harmful interference in a residential installation. This equipment generates, uses and can radiate radio frequency energy and, if not installed and used in accordance with the instructions, may cause harmful interference to radio communications. However, there is no guarantee that interference will not occur in a particular installation. If this equipment does cause harmful interference to radio or television reception, which can be determined by turning the equipment off and on, the user is encouraged to try to correct the interference by one or more of the measures listed below.

- † Reorient or relocate the receiving antenna.

- † Increase the separation between the equipment and receiver.

- † Connect the equipment into an outlet on a circuit different from that to which the receiver is connected.

- † Consult the dealer or an experienced radio/television technician for help.

#### Notice 1

The changes or modifications not expressly approved by the party responsible for compliance could void the user's authority to operate the equipment.

#### Notice 2

Shielded interface cables and A.C. power cord, if any, must be used in order to comply with the emission limits.

VOIR LA NOTICE D'INSTALLATION AVANT DE RACCORDER AU RESEAU.

This device complies with Part 15 of the FCC Rules. Operation is subject to the following two conditions:

- (1) this device may not cause harmful interference, and

- (2) this device must accept any interference received, including interference that may cause undesired operation.

# Chapter 1 Product Overview

Thank you for choosing the 2807780 Mini ITX mainboard from Gobal American, Inc.

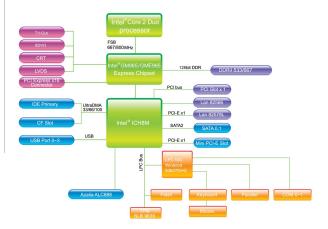

Based on the innovative Intel® GM965/GME965 & CH8M controllers for optimal system efficiency, the 2807780 accommodates the latest Intel® Core 2 Duo/Core Duo/Celeron M processors in Socket P and supports two 240-pin 533/667 MHz DDR2 DIMM slots to provide the maximum of 4GB memory capacity.

In the entry-level and mid-range market segment, the 2807780 can provide a high-performance solution for today's front-end and general purpose workstation, as well as in the future.

# **Mainboard Specifications**

#### Process or

- Intel Core 2 Duo/Core Duo/Celeron M CPU in Socket P

- Supports 3-pin CPU fan pin-header with Fan Speed Control

- Supports Intel Dual Core Technology to 533/667/800MHz and up

#### Supported FSB

- 533/667/800MHz

#### Chipset

- North Bridge: Intel GM965/GME965 chipset

- South Bridge: Intel ICH 8M chipset

#### Memory

- DDR 2 533/667 S DR AM (4GB Max)

- 2 DDR 2 DIMM slots (240pin / 1.8V)

#### LAN

- Supports 2 Gb Ethernet by Intel 82573L & 82566 DC

#### \_\_\_ Audio

- HDA Codec by Realtek ALC888 7.1 channel

- Compliant with Azalia 1.0 specs

- 6 watt amplifier

#### IDE

- 1 IDE port by ICH8M

- Supports Ultra DMA 66/100 mode

- Supports PIO, Bus Master operation mode

#### SATA

- S ATA II ports by IC H8M

- Supports two SATA II devices

- Supports storage and data transfers at up to 300MB/s

#### Connectors

#### Back Panel

- 2 R J-45 LAN iacks

- 4 USB 2.0 ports

- 1 D-S ub VGA connector

- 1 serial port

- 1 PS2 keyboard/mouse port

- 6 audio jacks

#### Onboard Connectors

- 2 USB 2.0 connectors (4 ports)

- 1 parallel port connector

- 1 SPDIF connector

- 1 LVDS connector

- 1 TV-out connector

- 1 digital I/O connector (16GPIO)

- 1 serial port connector

- 1 front panel connector

- 1 amplifier connector (4-pin)

#### Slots

- 1 PCI Express x16 slot

- 1 Mini PCI-E slot

- 1 PCI 32-bit/33MHz slot

- 1 CF socket

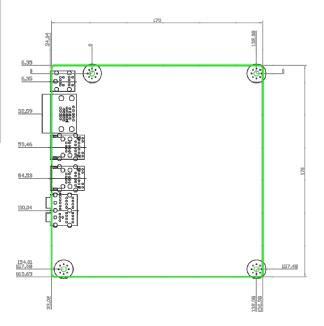

#### Form Factor

- Mini ITX: 170mm x 170mm

#### ■ Mounting

- 4 mounting holes

#### Environmental

- Storage Temperature

- Temperature: -20°C ~ 80°C

- Humidity: 0% RH ~ 95% RH

#### Operation Temperature

- Temperature: 0°C ~ 55°C

- Humidity: 0% RH ~ 85% RH

# **Block Diagram**

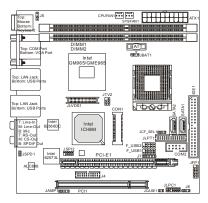

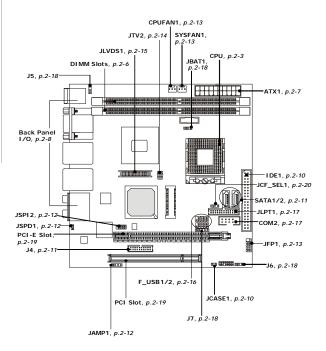

# **Mainboard Layout**

(2807780 v1.X) Mini ITX Mainboard

1-5

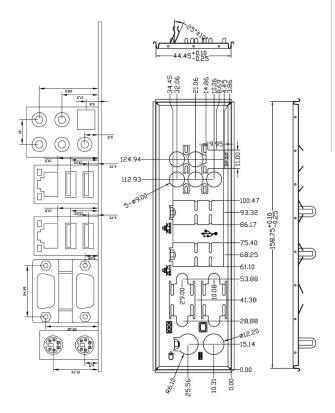

# **Board Dimension**

# Back Panel & I/O Shield Drawing

# **Power Consumption**

| Component        | Description                             |

|------------------|-----------------------------------------|

| CPU              | Intel Core 2 Duo T7100 processor        |

| Memory           | Kingston 2G DDR2-667 x2                 |

| Add-On VGA       | Nvidia FX1400 PCI-Express VGA Card x1   |

| Hard Disk        | Seagate 500G SATA2 7200rpm HDD x1       |

| Operating system | Microsoft® Windows XP® Professional SP2 |

| 2807780                                                                     |            | 3.3V       | 5V         | 12V Main                | 5V Standby | (-)12V     |

|-----------------------------------------------------------------------------|------------|------------|------------|-------------------------|------------|------------|

|                                                                             | Current(A) | Current(A) | Current(A) | Connector<br>Current(A) | Current(A) | Current(A) |

| Enter DOS(Stable)                                                           | 2.45       | 2.75       | 2.97       | 0                       | 0.05       | 0.02       |

| Enter BIOS(Stable)                                                          | 2.42       | 2.74       | 2.97       | 0                       | 0.05       |            |

| Idle                                                                        | 1.64       | 2.37       | 1.92       | 0                       | 0.05       | 0.01       |

| CPU Stress 100%                                                             | 1.66       | 2.7        | 3.5        | 0                       | 0.05       | 0.02       |

| Windows stress(3dMARK2006)                                                  | 1.66       | 3.22       | 4.5        | 0                       | 0.05       | 0.02       |

| Windows Desktop Standby S1<br>with/without two LANs connected<br>(stable)   | 1.08/1.07  | 1.78/1.76  | 1.58/1.56  | 0                       | 0.08/0.080 | 0.02       |

| Windows Desktop Standby S3<br>with/without two LANs connected<br>(stable)   | 0          | 0          | 0          | 0                       | 0.45/0.44  | 0          |

| Windows Desktop Hibernate S4<br>with/without two LANs connected<br>(stable) | 0          | 0          | 0          | 0                       | 0.25/0.24  | 0          |

| Windows Desktop Soft Off S5<br>with/without two LANs connected<br>(stable)  | 0          | 0          | 0          | 0                       | 0.25/0.24  | 0          |

# Safety Compliance & MTBF

| Certification |          | Standard number                          | Title of standard               |

|---------------|----------|------------------------------------------|---------------------------------|

|               |          | EN 55022:1998+A1:2000+A2:2003 Class B    | Product family standard         |

|               |          | EN 6100-3-2:2000 Class D                 | Limits for harmonic current     |

|               | RFI      | E14 0100-3-2.2000 Cla33 D                | emission                        |

| CE            |          |                                          | Limitation of voltage           |

|               |          | EN 6100-3-3:1995+A1:2001                 | fluctuation and flicker in low- |

|               |          |                                          | voltage supply system           |

|               | Immunity | EN 55024:1998+A1:2001+A2:2003            | Product family standard         |

| BSMI          | CNS 1343 | 88 乙類(1997年版)                            |                                 |

| C-Tick        | AS/NZS ( | CISPR 22:2004                            |                                 |

| FCC           | FCC CFR  | Title 47 Part 15 Subpart B: 2005 Class B |                                 |

| FCC           | CISPR 22 | 2: 2005                                  |                                 |

| VCCI          | VCCI V-3 | 2004, Class B                            |                                 |

| VCCI          | VCCI V-4 | 2004, Class B                            |                                 |

#### MTBF - Reliability Prediction

| Calculation Model | Operation       | Operating                              | Duty Cycle    | MTBF (hr.) |  |

|-------------------|-----------------|----------------------------------------|---------------|------------|--|

| Calculation Model | temperature (℃) | Environment                            | Duty Cycle    |            |  |

| Telcordia Issue 1 | 35              | GF, GU - Ground Fixed,<br>Uncontrolled | 10,867.351095 | 92,019     |  |

| MIL-HDBK-217 FN2  | 55              | GF, GU - Ground Fixed,<br>Uncontrolled | 117.312341    | 8,524      |  |

# Chapter 2 Hardware Setup

This chapter provides you with the information about hardware setup procedures. While doing the installation, be careful in holding the components and follow the installation procedures. For some components, if you install in the wrong orientation, the components will not work properly.

Use a grounded wrist strap before handling computer components. Static electricity may damage the components.

# **Quick Components Guide**

# **CPU (Central Processing Unit)**

The mainboard supports Intel® Core 2 Duo/Core Duo/Celeron M processors in Socket P. When you are installing the CPU, make sure the CPU has a heat sink and a cooling fan attached on the top to prevent overheating. If you do not have the heat sink and cooling fan, contact your dealer to purchase and install them before turning on the computer.

### **Important**

- Overheating will seriously damage the CPU and system. Always make sure the cooling fan can work properly to protect the CPU from overheating.

- Make sure that you apply an even layer of heat sink paste (or thermal tape) between the CPU and the heatsink to enhance heat dissipation.

- While replacing the CPU, always turn off the power supply or unplug the power supply's power cord from the grounded outlet first to ensure the safety of CPU.

#### CPU & Cooler Installation for Socket P

Locate the CPU socket on the mainboard.

- Place the CPU on top of the socket. Make sure to align the gold arrow on the CPU with the arrow key on the socket.

- 3. Push the CPU down until its pins securely fit into the socket.

4. On the front end of the CPU socket is a locking mechanism designed into the form of a screw head. Make sure that you actuate or deactuate this mechanism with a screwdriver before and after installing the CPU.

- 5. Flip over the mainboard and locate the position of the CPU socket.

- 6. Install the backplate to the back of the CPU socket with holes aligned.

CPU cooler backplate

- 7. The heatsink paste helps to enhance heat dissipation of the CPU. Before installing the cooler set (fan & heatsink bundled), make sure that you detach the shield of the heatsink paste under the cooler set.

- Locate the four screw holes around the CPU socket where the CPU cooler backplate was installed. Align the cooler set with the screw holes and mount it on top of the CPU.

9. Screw to secure the cooler set to the mainboard.

Connect the fan power cable to the CPUFAN1 connector on the mainboard.

# Memory

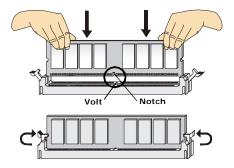

The DIMM slots are intended for system memory modules.

#### Installing DDR2 Modules

- The memory module has only one notch on the center and will only fit in the right orientation.

- Insert the memory module vertically into the DIMM slot. Then push it in until the golden finger on the memory module is deeply inserted in the DIMM slot.

You can barely see the golden finger if the memory module is properly inserted in the DIMM slot.

3. The plastic clip at each side of the DIMM slot will automatically close.

# **Power Supply**

#### ATX 20-Pin System Power Connector: ATX1

This connector allows you to connect to an ATX power supply. To connect to the ATX power supply, make sure the plug of the power supply is inserted in the proper orientation and the pins are aligned. Then push down the power supply firmly into the connector.

ATX1 Pin Definition

| PIN | SIGNAL | PIN | SIGNAL |

|-----|--------|-----|--------|

| 1   | 3.3V   | 11  | 3.3V   |

| 2   | 3.3V   | 12  | -12V   |

| 3   | GND    | 13  | GND    |

| 4   | 5V     | 14  | PS_ON  |

| 5   | GND    | 15  | GND    |

| 6   | 5V     | 16  | GND    |

| 7   | GND    | 17  | GND    |

| 8   | PW_OK  | 18  | -5V    |

| 9   | 5V_SB  | 19  | 5V     |

| 10  | 12V    | 20  | 5V     |

|     |        |     |        |

#### **Important**

Power supply of **350watts** (and above) is highly recommended for system stability.

# **Back Panel**

VGA Port USB Ports

**USB Ports**

MIC Optical SPDIF-Out

#### ▶ Mouse/Keyboard

The standard PS/2® mouse/keyboard DIN connector is for a PS/2® mouse/keyboard.

#### ▶ Serial Port

The serial port is a 16550A high speed communications port that sends/ receives 16 bytes FIFOs. You can attach a serial mouse or other serial devices directly to the connector.

#### ► VGA Port

The DB15-pin female connector is provided for monitor.

#### ► USB Port

The USB (Universal Serial Bus) port is for attaching USB devices such as keyboard, mouse, or other USB-compatible devices.

#### ► LAN

The standard RJ-45 LAN jack is for con-Link Indicator nection to the Local Area Network (LAN). 10000 You can connect a network cable to it.

| LED   | Color  | LED State               | Condition                                                       |

|-------|--------|-------------------------|-----------------------------------------------------------------|

|       |        | Off                     | LAN link is not established.                                    |

| Left  | Orange | On (steady state)       | LAN link is established.                                        |

|       |        | On (brighter & pulsing) | The computer is communicating with another computer on the LAN. |

|       | Green  | Off                     | 10 Mbit/sec data rate is selected.                              |

| Right |        | On                      | 100 Mbit/sec data rate is selected.                             |

|       | Orange | On                      | 1000 Mbit/sec data rate is selected.                            |

#### ► Audio Ports

These audio connectors are used for audio devices. You can differentiate the color of the audio jacks for different audio sound effects.

- Line-In (Blue) Line In / Side-Surround Out in 7.1 channel mode, is used for external CD player, tapeplayer or other audio devices.

- Line-Out (Green) Line Out, is a connector for speakers or headphones.

Mic (Pink) Mic. is a connector for microphones.

- RS-Out (Black) Rear-Surround Out in 4/5.1/7.1 channel mode.

- CS-Out (Orange) Center/ Subwoofer Out in 5.1/7.1 channel mode.

#### ▶ Optical S/PDIF-Out

This SPDIF (Sony & Philips Digital Interconnect Format) connector is provided for digital audio transmission to external speakers through an optical fiber cable.

# Connector

#### Chassis Intrusion Connector: JCASE1

This connector connects to the chassis intrusion switch cable. If the chassis is opened, the chassis intrusion mechanism will be activated. The system will record this status and show a warning message on the screen. To clear the warning, you must enter the BIOS utility and clear the record.

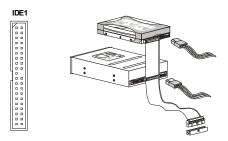

# IDE Connector: IDE1

This connector supports IDE hard disk drives, optical disk drives and other IDE devices.

#### **Important**

If you install two IDE devices on the same cable, you must configure the drives separately to master / slave mode by setting jumpers. Refer to IDE device's documentation supplied by the vendors for jumper setting instructions.

#### Digital IO Connector: J4

The J4 is designed to connect the General-Purpose Input/Output (GPIO) peripheral module.

#### Pin Definition

|              |  |  | J | 4 |  |  |   |   |

|--------------|--|--|---|---|--|--|---|---|

| 19 [<br>20 [ |  |  |   |   |  |  | 7 | 1 |

| Fill Delillition |          |     |          |  |  |  |

|------------------|----------|-----|----------|--|--|--|

| PIN              | SIGNAL   | PIN | SIGNAL   |  |  |  |

| 1                | VCC3     | 2   | VCC5     |  |  |  |

| 3                | N_GPIO10 | 4   | N_GPIO20 |  |  |  |

| 5                | N_GPIO11 | 6   | N_GPI021 |  |  |  |

| 7                | N_GPI012 | 8   | N_GPI022 |  |  |  |

| 9                | N_GPI013 | 10  | N_GPIO23 |  |  |  |

| 11               | N_GPI014 | 12  | N_GPIO24 |  |  |  |

| 13               | N_GPI015 | 14  | N_GPIO25 |  |  |  |

| 15               | N_GPIO16 | 16  | N_GPIO26 |  |  |  |

| 17               | N_GPI017 | 18  | N_GPIO27 |  |  |  |

| 19               | GND      | 20  | NC       |  |  |  |

|                  |          |     |          |  |  |  |

#### Serial ATA II Connector: SATA1, SATA2

This connector is a high-speed Serial ATA II interface port. Each connector can connect to one Serial ATA II device

#### SATA2 SATA1

#### **Important**

Please do not fold the Serial ATA cable into 90-degree angle. Otherwise, data loss may occur during transmission.

#### **Audio Amplifier Connector: JAMP1**

The JAMP1 is used to connect audio amplifiers to enhance audio performance.

#### Pin Definition

JAMP1

# S/PDIF-Out Connector: JSPD1 (Optional, for HDMI graphics card only)

This connector is used to connect S/PDIF (Sony & Philips Digital Interconnect Format) interface for digital audio transmission to the HDMI graphics card.

# SPI Flash ROM Connector: JSPI2

This connector is used to flash SPI flash ROM.

#### Pin Definition

| Pin | Description | Pin | Description |

|-----|-------------|-----|-------------|

| 1   | VCC3_SB     | 2   | VCC3_SB     |

| 3   | SPI_MISO_F  | 4   | SPI_MOSI_F  |

| 5   | SPI_CS0_F#  | 6   | SPI_CLK_F   |

| 7   | GND         | 8   | GND         |

| 9   | SPI_HOLD#   | 10  | NC          |

#### Fan Power Connectors: CPUFAN1, SYSFAN1

The fan power connectors support system cooling fan with +12V. When connecting the wire to the connectors, always note that the red wire is the positive and should be connected to the +12V; the black wire is Ground and should be connected to GND. If the mainboard has a System Hardware Monitor chipset on-board, you must use a specially designed fan with speed sensor to take advantage of the CPU fan control.

#### **Important**

Please refer to the recommended CPU fans at Intel® official website or consult the vendors for proper CPU cooling fan.

#### Front Panel Connector: JFP1

The mainboard provides one front panel connector for electrical connection to the front panel switches and LEDs. The JFP1 is compliant with Intel® Front Panel I/O Connectivity Design Guide.

JFP1 Pin Definition

| PIN | SIGNAL    | DESCRIPTION                                 |

|-----|-----------|---------------------------------------------|

| 1   | HD_LED+   | Hard disk LED pull-up                       |

| 2   | FPPWR/SLP | MSG LED pull-up                             |

| 3   | HD_LED -  | Hard disk active LED                        |

| 4   | FPPWR/SLP | MSG LED pull-up                             |

| 5   | RST_SW-   | Reset Switch low reference pull-down to GND |

| 6   | PWR_SW+   | Power Switch high reference pull-up         |

| 7   | RST_SW+   | Reset Switch high reference pull-up         |

| 8   | PWR_SW-   | Power Switch low reference pull-down to GND |

| 9   | RSVD_DNU  | Reserved. Do not use.                       |

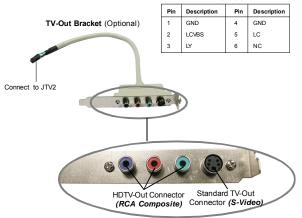

#### TV-Out Connector: JTV2 (Optional)

This connector is for you to attach an optional TV-Out bracket that offers two types of TV-Out connectors: S-Video and RCA Composite connectors. Select the appropriate one to connect the standard television or the HDTV (High-Definition TeleVision).

| Display Watrix |     |      |        |      |                   |  |

|----------------|-----|------|--------|------|-------------------|--|

|                | CRT | LVDS | TV-OUT | SDVO | PCI-E x16<br>port |  |

| CRT            | /   | ٧    | ٧      | ٧    | х                 |  |

| LVDS           | ٧   |      | ٧      | ٧    | х                 |  |

| TV-OUT         | ٧   | ٧    | /      | ٧    | Х                 |  |

| SDVO           | ٧   | V    | ٧      | /    | Х                 |  |

| PCI-E x16 port | Х   | X    | X      | Х    |                   |  |

V : Support X : No Support

#### Pin Definition

# Important

Please note that the TV-Out bracket can connect to one TV only. Users have to choose either the RCA Composite or the S-Video to connect. Simultaneously connecting two TVs to this bracket is prohibited and may lead to the malfunction of the TVs.

#### LVDS Flat Panel Connector: JLVDS1

The LVDS (Low Voltage Differential Signal) connector provides a digital interface typically used with flat panels. After connecting an LVDS interfaced flat panel to the JLVDS1, be sure to check the panel datasheet and set the J7 LVDS Power Selection Jumper (p. 2-18) to a proper voltage.

#### Display Matrix PCI-E x16 CRT LVDS TV-OUT SDVO port ν CRT ν ν х LVDS х TV-OUT ν х SDVO v ν x PCI-E x16 port

| <b>v</b> : | Support | X : No Support |

|------------|---------|----------------|

|            |         |                |

| SIGNAL     | Р  | IN | SIGNAL    |

|------------|----|----|-----------|

| +12V       | 2  | 1  | +12V      |

| +12V       | 4  | 3  | +12V      |

| GND        | 6  | 5  | +12V      |

| GND        | 8  | 7  | VCC3/VCC5 |

| LCD_VDD    | 10 | 9  | LCD_VDD   |

| LDDC_DATA  | 12 | 11 | LDDC_CLK  |

| LVDS_VDDEN | 14 | 13 | L_BKLTCTL |

| GND        | 16 | 15 | L_BKLTEN  |

| LA_DATA0   | 18 | 17 | LA_DATA0# |

| LA_DATA1   | 20 | 19 | LA_DATA1# |

| LA_DATA2   | 22 | 21 | LA_DATA2# |

| LA_CLK     | 24 | 23 | LA_CLK#   |

| LA_DATA3   | 26 | 25 | LA_DATA3# |

| GND        | 28 | 27 | GND       |

| LB_DATA0   | 30 | 29 | LB_DATA0# |

| LB_DATA1   | 32 | 31 | LB_DATA1# |

| LB_DATA2   | 34 | 33 | LB_DATA2# |

| LB_CLK     | 36 | 35 | LB_CLK#   |

| LB_DATA3   | 38 | 37 | LB_DATA3# |

| GND        | 40 | 39 | GND       |

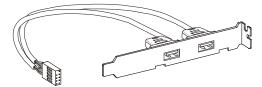

#### Front USB Connector: F\_USB1, F\_USB2

This connector, compliant with Intel® I/O Connectivity Design Guide, is ideal for connecting high-speed USB interface peripherals such as USB HDD, digital cameras, MP3 players, printers, modems and the like.

#### Pin Definition

| PIN | SIGNAL       | PIN | SIGNAL |

|-----|--------------|-----|--------|

| 1   | VCC          | 2   | VCC    |

| 3   | USB0-        | 4   | USB1-  |

| 5   | USB0+        | 6   | USB1+  |

| 7   | GND          | 8   | GND    |

| 9   | Key (no pin) | 10  | NC     |

#### USB 2.0 Bracket (Optional)

# Important

Note that the pins of VCC and GND must be connected correctly to avoid possible damage.

#### Serial Port Connector: COM 2

This connector is a 16550A high speed communications port that sends/receives 16 bytes FIFOs. You can attach a serial device to it through the optional serial port bracket.

| PIN | SIGNAL   | DESCRIPTION                 |

|-----|----------|-----------------------------|

| 1   | DCD      | Data Carry Detect           |

| 2   | SIN      | Serial In or Receive Data   |

| 3   | SOUT     | Serial Out or Transmit Data |

| 4   | DTR      | Data Terminal Ready         |

| 5   | GND      | Ground                      |

| 6   | DSR      | Data Set Ready              |

| 7   | RTS      | Request To Send             |

| 8   | CTS      | Clear To Send               |

| 9   | VCC_COM3 | PowerSource                 |

#### Parallel Port Connector: JLPT1

The mainboard provides a 26-pin header for connection to an optional parallel port bracket. The parallel port is a standard printer port that supports Enhanced Parallel Port (EPP) and Extended Capabilities Parallel Port (ECP) mode.

| Pin | Signal Name | Pin | Signal Name |

|-----|-------------|-----|-------------|

| 1   | RSTB#       | 2   | AFD#        |

| 3   | PRND0       | 4   | ERR#        |

| 5   | PRND1       | 6   | PINIT#      |

| 7   | PRND2       | 8   | LPT_SLIN#   |

| 9   | PRND3       | 10  | GND         |

| 11  | PRND4       | 12  | GND         |

| 13  | PRND5       | 14  | GND         |

| 15  | PRND6       | 16  | GND         |

| 17  | PRND7       | 18  | GND         |

| 19  | ACK#        | 20  | GND         |

| 21  | BUSY        | 22  | GND         |

| 23  | PE          | 24  | GND         |

| 25  | SLCT        | 26  | GND         |

Parallel/Serial Port Bracket (Optional)

# **Jumper**

#### LVDS Power Selection Jumper: J7

Use this jumper to specify the operation voltage of the LVDS interfaced flat panel.

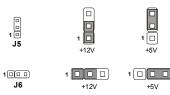

#### COM Port Power Jumpers: J5. J6

These jumpers specify the operation voltage of the onboard serial ports.

#### Clear CMOS Jumper: JBAT1

There is a CMOS RAM onboard that has a power supply from external battery to keep the data of system configuration. With the CMOS RAM, the system can automatically boot OS every time it is turned on. If you want to clear the system configuration, set this jumper to clear data.

#### **Important**

You can clear CMOS by shorting 1-2 pin while the system is off. Then return to 2-3 pin position. Avoid clearing the CMOS while the system is on; it will damage the mainboard.

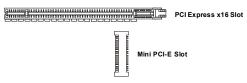

#### PCI (Peripheral Component Interconnect) Express Slot

The PCI Express slot supports PCI Express interface expansion cards. The PCI Express x 16 slot supports up to 4.0 GB/s transfer rate.

The CON1 is Mini PCI-E connector for wireless LAN, TV tuner, and Robson NAND Flash

### PCI (Peripheral Component Interconnect) Slot

The PCI slot supports LAN card, SCSI card, USB card, and other add-on cards that comply with PCI specifications.

#### PCI Interrupt Request Routing

The IRQ, acronym of interrupt request line and pronounced I-R-Q, are hardware lines over which devices can send interrupt signals to the microprocessor. The PCI IRQ pins are typically connected to the PCI bus pins as follows:

| DEVICE           | INT Pin | IDSEL | CLOCK    | REQ# / GNT#   |

|------------------|---------|-------|----------|---------------|

| 32-bit PCI Slot  | PIRQA   | AD17  | PCICLK 0 | REQ#0 / GNT#0 |

| 32-bit PCI Riser | PIRQC   | AD18  | PCICLK 1 | REQ#1 / GNT#1 |

| 32-bit PCI Riser | PIRQD   | AD19  | PCICLK 2 | REQ#2 / GNT#2 |

# **Important**

When adding or removing expansion cards, make sure that you unplug the power supply first. Meanwhile, read the documentation for the expansion card to configure any necessary hardware or software settings for the expansion card, such as jumpers, switches or BIOS configuration.

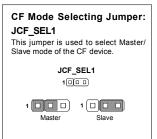

#### CompactFlash Card Slot: CF1

This CompactFlash slot shares one channel of the IDE controller. You can install one CompactFlash typel / type II device.

#### **Important**

- \* The CF1 slot and the IDE1 connector shares and uses the same channel. CF1 and IDE1 can support up to 2 IDE devices without CF device or 1 IDE device with 1 CF device.

- \* If you install two IDE devices, you must configure the second drive to Slave mode by setting its jumper. Refer to the hard disk documentation supplied by hard disk vendors for jumper setting instructions.

- \* If you install one IDE device with ATA133 IDE cable and one CF device, you must configure the CF drive to Master mode by setting jumper JCF\_SEL1. CF only supports Master mode by using the ATA133 IDE cable.

- \* CF only supports Slave mode by using ATA33 IDE cable.

# Chapter 3 Sys tem Resources

This chapter provides information on the following system resources:

- 1. Watch Dog Timer Setting (p.3-2);

- 2. AMI POST Code (p.3-3);

- 3. Resource List (p.3-7).

# **Watch Dog Timer Setting**

#### Software code

SIO\_IDX equ 2EH SIO\_DTA equ 2FH

Timer equ 10; reset after 10 seconds

- Enter configuration mode mov dx,SIO\_IDX mov al,87h out dx,al out dx,al

- 2. Set to LDN 08 mov dx,SIO\_IDX mov al,07h out dx,al mov dx,SIO\_DTA mov al,08h out dx.al

- 3. Set WatchDog Timer mov dx,SIO\_IDX mov al,0f6h out dx,al mov dx,SIO\_DTA mov al,Timer out dx.al

- Exit configuration mode movdx,SIO\_IDX mov al,0AAh out dx,al

# **AMI POST Code**

#### **Bootblock Initialization Code Checkpoints**

The Bootblock initialization code sets up the chipset, memory and other components before system memory is available. The following table describes the type of checkpoints that may occur during the bootblock initialization portion of the BIOS:

| Checkpoint | Description                                                                                                                                                                                 |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Before D1  | Early chipset initialization is done. Early super I/O initialization is done including RTC and keyboard controller. NMI is disabled.                                                        |

| D1         | Perform keyboard controller BAT test. Check if waking up from power management suspend state. Save power-on CPUID value in scratch CMOS.                                                    |

| D0         | Go to flat mode with 4GB limit and GA20 enabled. Verify the bootblock checksum.                                                                                                             |

| D2         | Disable CACHE before memory detection. Execute full memory sizing module. Verify that flat mode is enabled.                                                                                 |

| D3         | If memory sizing module not executed, start memory refresh and do memory sizing in Bootblock code. Do additional chipset initialization. Re-enable CACHE. Verify that flat mode is enabled. |

| D4         | Test base 512KB memory. Adjust policies and cache first 8MB. Set stack.                                                                                                                     |

| D5         | Bootblock code is copied from ROM to lower system memory<br>and control is given to it. BIOS now executes out of RAM.                                                                       |

| D6         | Both key sequence and OEM specific method is checked to determine if BIOS recovery is forced. Main BIOS checksum is tested. If BIOS recovery is necessary, control flows to checkpoint EO.  |

| D7         | Restore CPUID value back into register. The Bootblock-<br>Runtime interface module is moved to system memory and<br>control is given to it. Determine whether to execute serial<br>flash.   |

| D8         | The Runtime module is uncompressed into memory. CPUID information is stored in memory.                                                                                                      |

| D9         | Store the Uncompressed pointer for future use in PMM. Copying Main BIOS into memory. Leaves all RAM below 1MB Read-Write including E000 and F000 shadow areas but closing SMRAM.            |

| DA         | Restore CPUID value back into register. Give control to BIOS POST (ExecutePOSTKernel). See POST Code Checkpoints section of document for more information.                                  |

# POST Code Checkpoints

The POST code checkpoints are the largest set of checkpoints during the BIOS preboot process. The following table describes the type of checkpoints that may occur during the POST portion of the BIOS:

| Checkpoint | Description                                                                                                                                                                                                                                                                                                                                                                                                       |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 03         | Disable NMI, Parity, video for EGA, and DMA controllers.<br>Initialize BIOS, POST, Runtime data area. Also initialize BIOS<br>modules on POST entry and GPNV area. Initialized CMOS as<br>mentioned in the Kernel Variable "wCMOSFlags."                                                                                                                                                                          |

| 04         | Check CMOS diagnostic byte to determine if battery power is<br>OK and CMOS checksum is OK. Verify CMOS checksum manually by reading storage area. If the CMOS checksum is<br>bad, update CMOS with power-on default values and clear<br>passwords. Initialize status register A. Initializes data variables that are based on CMOS setup<br>questions. Initializes both the 8259 compatible PICs in the<br>system |

| 05         | Initializes the interrupt controlling hardware (generally PIC) and interrupt vector table.                                                                                                                                                                                                                                                                                                                        |

| 06         | Do R/W test to CH-2 count reg. Initialize CH-0 as system timer. Install the POSTINT1Ch handler. Enable IRQ-0 in PIC for system timer interrupt.  Traps INT1Ch vector to "POSTINT1ChHandlerBlock."                                                                                                                                                                                                                 |

| 08         | Initializes the CPU. The BAT test is being done on KBC. Program the keyboard controller command byte is being done after Auto detection of KB/MS using AMI KB-5.                                                                                                                                                                                                                                                  |

| 0A         | Initializes the 8042 compatible Key Board Controller.                                                                                                                                                                                                                                                                                                                                                             |

| OB         | Detects the presence of PS/2 mouse.                                                                                                                                                                                                                                                                                                                                                                               |

| OC         | Detects the presence of Keyboard in KBC port.                                                                                                                                                                                                                                                                                                                                                                     |

| 0E         | Testing and initialization of different Input Devices. Also, update the Kernel Variables.  Traps the INTO9h vector, so that the POST INTO9h handler gets control for IRQ1. Uncompress all available language, BIOS logo, and Silent logo modules.                                                                                                                                                                 |

# POST Code Checkpoints

| Checkpoint | Description                                                      |

|------------|------------------------------------------------------------------|

| 13         | Early POST initialization of chipset registers.                  |

| 24         | Uncompress and initialize any platform specific BIOS modules.    |

| 30         | Initialize System Management Interrupt.                          |

| 2A         | Initializes different devices through DIM.                       |

|            | See DIM Code Checkpoints section of document for more            |

|            | information.                                                     |

| 2C         | Initializes different devices. Detects and initializes the video |

|            | adapter installed in the system that have optional ROMs.         |

| 2E         | Initializes all the output devices.                              |

| 31         | Allocate memory for ADM module and uncompress it. Give           |

|            | control to ADM module for initialization. Initialize language    |

|            | and font modules for ADM. Activate ADM module.                   |

| 33         | Initializes the silent boot module. Set the window for           |

|            | displaying text information.                                     |

| 37         | Displaying sign-on message, CPU information, setup key           |

|            | message, and any OEM specific information.                       |

| 38         | Initializes different devices through DIM. See DIM Code          |

|            | Checkpoints section of document for more information.            |

| 39         | Initializes DMAC-1 & DMAC-2.                                     |

| 3A         | Initialize RTC date/time.                                        |

| 3B         | Test for total memory installed in the system. Also, Check for   |

|            | DEL or ESC keys to limit memory test. Display total memory       |

|            | in the system.                                                   |

| 3C         | Mid POST initialization of chipset registers.                    |

| 40         | Detect different devices (Parallel ports, serial ports, and      |

|            | coprocessor in CPU, etc.) successfully installed in the          |

|            | system and update the BDA, EBDAetc.                              |

| 50         | Programming the memory hole or any kind of implementation        |

| 30         | that needs an adjustment in system RAM size if needed.           |

| 52         | Updates CMOS memory size from memory found in memory             |

| J.         | test. Allocates memory for Extended BIOS Data Area from          |

|            | base memory.                                                     |

| 60         | Initializes NUM-LOCK status and programs the KBD typematic       |

| 00         | rate.                                                            |

| 75         | Initialize Int-13 and prepare for IPL detection.                 |

| 78         | Initializes IPL devices controlled by BIOS and option ROMs.      |

| 7A         | Initializes remaining option ROMs.                               |

| 7C         | Generate and write contents of ESCD in NVRam.                    |

| 84         | Log errors encountered during POST.                              |

| 85         | Display errors to the user and gets the user response for error. |

| 87         | Execute BIOS setup if needed / requested.                        |

| 8C         | Late POST initialization of chipset registers.                   |

| 8E         | Program the peripheral parameters. Enable/Disable NMI as         |

| OL.        | selected                                                         |

| 90         | Late POST initialization of system management interrupt.         |

| A0         | Check boot password if installed.                                |

| A0<br>A1   | Clean-up work needed before booting to OS.                       |

| A2         | Takes care of runtime image preparation for different BIOS       |

| AL         | modules. Fill the free area in F000h segment with 0FFh.          |

|            | modules. The the free area in robbit segment with UFFII.         |

# 2807780 Mainboard

|    | Initializes the Microsoft IRQ Routing Table. Prepares the runtime language module. Disables the system configuration display if needed. |

|----|-----------------------------------------------------------------------------------------------------------------------------------------|

| A4 | Initialize runtime language module.                                                                                                     |

| A7 | Displays the system configuration screen if enabled. Initialize the CPU's before boot, which includes the programming of the MTRR's.    |

| A8 | Prepare CPU for OS boot including final MTRR values.                                                                                    |

| A9 | Wait for user input at config display if needed.                                                                                        |

| AA | Uninstall POST INT1Ch vector and INT09h vector. Deinitializes the ADM module.                                                           |

| AB | Prepare BBS for Int 19 boot.                                                                                                            |

| AC | End of POST initialization of chipset registers.                                                                                        |

| B1 | Save system context for ACPI.                                                                                                           |

| 00 | Passes control to OS Loader (typically INT19h).                                                                                         |

# **Resource List**

#### Generic I/O Ports

#### (I) ICH8M GPIO

| Pin  | GPIO | Тур  | Multi       | Power | Connection.   |

|------|------|------|-------------|-------|---------------|

| AG12 | 0    | I/O  | BMBUSY#     | 3.3v  | PM_BMBUSY#    |

| AG22 | 11   | I/O  | SMBALERT#   | 3.3v  | SMB_ALERT#    |

| AE20 | 15   | I/OD | STP_PCI#    | 3.3v  | PM_STP_PCI#   |

| AG18 | 3    | I/OD | STP_CPU#    | 5v    | PM_STP_CPU#   |

| AH11 | 32   | I/OD | CLKRUN#     | 3.3v  | P_CLKRUN#     |

| AJ8  | 1    | I/OD | TACH1       | 3.3v  | NC            |

| AJ9  | 6    | I/O  | TACH2       | 3.3v  | NC            |

| AH9  | 7    | I/O  | TACH3       | 3.3v  | NC            |

| AE16 | 8    | I/O  | GPIO8       | 3.3v  | SIO_PME#      |

| AC19 | 12   | I/O  | GPIO12      | 3.3v  | SPI_HOLD_GPO# |

| AG8  | 17   | I/O  | TACH0       | 3.3v  | SPI_WP#       |

| AH12 | 18   | I/O  | GPIO18      | 3.3v  | SLPBTIN#      |

| AE11 | 20   | I/O  | GPIO20      | 3.3v  | ATADET0       |

| AG10 | 22   | I/O  | SCLOCK      | 3.3v  | NC            |

| AH25 | 27   | I/O  | QRT_STATE0  | 3.3v  | EL_STATE0     |

| AD16 | 28   | I/O  | QRT_STATE1  | 3.3v  | EL_STATE1     |

| AG13 | 35   | I/O  | SATACLKREQ# | 3.3v  | CLK_SATA_OE#  |

| AF9  | 38   | I/O  | SLOAD       | 3.3v  | NC            |

| AJ11 | 39   | I/O  | SDATAOUT0   | 3.3v  | NC            |

| AD10 | 48   | I/O  | SDATAOUT1   | 3.3v  | NC            |

| AJ12 | 21   | I/O  | SATA0GP     | 3.3v  | RESISTOR      |

| AJ10 | 19   | I/O  | SATA1GP     | 3.3v  | RESISTOR      |

| AF11 | 36   | I/O  | SATA2GP     | 3.3v  | RESISTOR      |

| AG11 | 37   | I/O  | SATA3GP     | 3.3v  | RESISTOR      |

| AH27 | 26   | I/O  | S4_STATE#   | 3.3v  | NC            |

| AJ27 | 24   | I/O  | NCMEM_LED   | 3.3v  | LAN_EN        |

| AJ24 | 10   | I/O  | ME_EC_ALERT | 3.3v  | PHY_DIS#      |

| AF22 | 14   | I/O  | EC_ME_ALERT | 3.3v  | NC            |

| AG19 | 9    | I/O  | WOL_EN      | 3.3v  | NC            |

| AG16 | 40   | I/O  | OC1#        | 3.3v  | OC0#          |

| AG15 | 41   | I/O  | OC2#        | 3.3v  | OC0#          |

| AE15 | 42   | I/O  | OC3#        | 3.3v  | OC0#          |

| AF15 | 43   | I/O  | OC4#        | 3.3v  | OC1#          |

| AG17 | 29   | I/O  | OC5#        | 3.3v  | OC1#          |

| AD12 | 30   | I/O  | OC6#        | 3.3v  | OC1#          |

| AJ18 | 31   | I/O  | OC7#        | 3.3v  | OC1#          |

| SIO G | PIO  |     |                   |       |             |

|-------|------|-----|-------------------|-------|-------------|

| Pin   | GPIO | Тур | Multi             | Power | Connection. |

| 121   | 17   | I/O | VID7              | VCC5  | NC          |

| 122   | 16   | I/O | VID6              | VCC5  | NC          |

| 123   | 15   | I/O | VID5              | VCC5  | NC          |

| 124   | 14   | I/O | VID4              | VCC5  | NC          |

| 125   | 13   | I/O | VID3              | VCC5  | NC          |

| 126   | 12   | I/O | VID2              | VCC5  | NC          |

| 127   | 11   | I/O | VID1              | VCC5  | NC          |

| 128   | 10   | I/O | VID0              | VCC5  | NC          |

| 120   | 20   | 0   | CPUFANOUT1/GP20   | VCC   | CFAN_PWM    |

| 119   | 21   | I/O | CPUFANN1/GP21     | VCC   | CPU_FAN     |

| 89    | 33   | I/O | RSTOUT3#/GP33/SDA | VSB   | NC          |

| 90    | 32   | I/O | RSTOUT2#/GP32/SCL | VSB   | NC          |

| 91    | 31   | I/O | GP31              | VSB   | NC          |

| 92    | 30   | I/O | GP30              | VSB   | NC          |

| 67    | 57   | 0   | GP57/PSOUT#       | VSB   | PWRBTN#     |

| 68    | 56   | I   | GP56/PSIN#        | VSB   | IO_PWRBTN#  |

| 64    | 37   | I/O | GP37              | VSB   | NC          |

| 72    | 53   | I/O | GP53/PSON#        | VSB   | PS_ON#      |

| 73    | 52   | 1   | GP52/SUSB#        | VSB   | SLP_S3#     |

| 77    | 50   | I/O | WDTO#GP50         | VSB   | GP50        |

| 2     | 23   | I/O | SCK/GP23          | VCC   | NC          |

| 88    | 34   | 0   | RSTOUT4#GP34      | VSB   | NC          |

| 69    | 36   | I/O | GP36              | VSB   | NC          |

| 87    | 35   | I/O | GP35              | VSB   | NC          |

| 75    | 51   | 0   | RSMRST#           | VSB   | VCC3        |

| 56    | 61   | I   | DCDA#             | VCC   | DCDA#       |

| 50    | 66   | 1   | DDSRA#            | VCC   | DDSRA#      |

| 53    | 63   | I   | SINA              | VCC   | SINA        |

| 51    | 65   | I/O | RTSA#             | VCC   | RTSA#       |

| 54    | 62   | 0   | SOUTA             | VCC   | SOUTA       |

| 49    | 67   | I   | CTSA#             | VCC   | CTSA#       |

| 52    | 64   | 0   | DTRA#             | VCC   | DTRA#       |

| 57    | 60   | I   | RIA#              | VSB   | RIA#        |

| 84    | 41   | I   | DCDB#             | VSB   | DCDB#       |

#### System Resources

| 79 | 46 | I   | DSRB#  | VSB | DSRB#  |

|----|----|-----|--------|-----|--------|

| 82 | 43 | 1   | SINB   | VSB | SINB   |

| 80 | 45 | 0   | RTSB#  | VSB | RTSB#  |

| 83 | 42 | 0   | SOUTB  | VSB | SOUTB  |

| 78 | 47 | 1   | CTSB#  | VSB | CTSB#  |

| 81 | 44 | 0   | DTRB#  | VSB | DTRB#  |

| 85 | 40 | 1   | RIB#   | VSB | RIB#   |

| 63 | 26 | I/O | KBDAT# | VSB | KBDAT# |

| 62 | 27 | I/O | KBCLK# | VSB | KBCLK# |

| 66 | 24 | I/O | MSDAT# | VSB | MSDAT# |

| 65 | 25 | I/O | MSCLK# | VSB | MSCLK# |

| 70 | 55 | I/O | SUSLED | VSB | GND    |

| 71 | 54 | I/O | PWROK  | VSB | NC     |

#### I/O Map

| I/O Port   | Description                   |

|------------|-------------------------------|

| 0000-000F  | DMA Controller 1              |

| 0020-0021  | Interrupt Controller 1        |

| 002E-002F  | SIO Port                      |

| 0040-0043  | ystem Timer                   |

| 004E-004F  | TPM Port                      |

| 0060, 0064 | Keyboard Controller           |

| 0070-0073  | RTC and CMOS                  |

| 0080-0090  | DMA Controller Page Registers |

| 0092       | Port 92h                      |

| 00A0-00A1  | Interrupt Controller 2        |

| 00B2-00B3  | APM register                  |

| 00C0-00DF  | DMA Controller 2              |

| 00F0-00FF  | Numeric Data Processor        |

| 01F0-01F7  | Primary IDE Controller        |

| 02F8-02FF  | COM2                          |

| 0376       | Secondary IDE Controller      |

| 0378-037F  | LPT1                          |

| 03F6       | Primary IDE Controller        |

| 03F8-03FF  | COM1                          |

| 0400-045F  | ACPI I/O space                |

| 0500-050F  | SMBus I/O Space               |

| 0CF8-0CFF  | PCI configuration Port        |

#### System Resources

#### PCI Devices

| PCI Device                    |         |         |      |      |       |

|-------------------------------|---------|---------|------|------|-------|

| Device                        | Ven. ID | Dev. ID | Bus# | Dev# | Func# |

| Host Bridge                   | 8086    | 2A00    | 00   | 00   | 00    |

| VGA-compatible Controller     | 8086    | 2A02    | 00   | 02   | 00    |

| Other Display Controller      | 8086    | 2A03    | 00   | 02   | 01    |

| Ethernet Controller           | 8086    | 104B    | 00   | 19   | 00    |

| UHCI USB Controller           | 8086    | 2834    | 00   | 1A   | 00    |

| UHCI USB Controller           | 8086    | 2835    | 00   | 1A   | 01    |

| Unknown Device                | 8086    | 283A    | 00   | 1A   | 07    |

| Unknown Device                | 8086    | 284B    | 00   | 1B   | 00    |

| PCI-to-PCI Bridge             | 8086    | 283F    | 00   | 1C   | 00    |

| UHCI USB Controller           | 8086    | 2830    | 00   | 1D   | 00    |

| UHCI USB Controller           | 8086    | 2831    | 00   | 1D   | 01    |

| UHCI USB Controller           | 8086    | 2832    | 00   | 1D   | 02    |

| Unknown Device                | 8086    | 2836    | 00   | 1D   | 07    |

| Subtractive Decode P2P Bridge | 8086    | 2448    | 00   | 1E   | 00    |

| ISA Bridge                    | 8086    | 2815    | 00   | 1F   | 00    |

| IDE Controller                | 8086    | 2850    | 00   | 1F   | 01    |

| IDE Controller                | 8086    | 2828    | 00   | 1F   | 02    |

| Smbus                         | 8086    | 283E    | 00   | 1F   | 03    |

#### SMBus Resource Allocation

| SMBus Resource Allocation |                     |                 |  |  |

|---------------------------|---------------------|-----------------|--|--|

| Device                    | Address Description |                 |  |  |

| MS-7                      | 0101 111X           | ACPI Controller |  |  |

| DIMM Slot                 | 1010 0000           | SPD             |  |  |

#### ISA Interrupt Allocation

| ISA Interrupt Allocation |                           |  |  |

|--------------------------|---------------------------|--|--|

| IRQ                      | Description               |  |  |

| IRQ0                     | System Timer              |  |  |

| IRQ1                     | Keyboard Controller       |  |  |

| IRQ2                     | Cascade Interrupt         |  |  |

| IRQ3                     | COM2                      |  |  |

| IRQ4                     | COM1                      |  |  |

| IRQ5                     | PCI Device                |  |  |

| IRQ6                     | PCI Device                |  |  |

| IRQ7                     | LPT1                      |  |  |

| IRQ8                     | RTC                       |  |  |

| IRQ9                     | ACPI Controller Interrupt |  |  |

| IRQ10                    | PCI Device                |  |  |

| IRQ11                    | PCI Device                |  |  |

| IRQ12                    | PS/2 Mouse                |  |  |

| IRQ13                    | Numeric Data Processor    |  |  |

| IRQ14                    | Primary IDE Controller    |  |  |

| IRQ15                    | Secondary IDE Controller  |  |  |

#### ISA DMA Channel Allocation

| DMA Channel | Description               |

|-------------|---------------------------|

| Channel 0   | Unassigned 8-bit channel  |

| Channel 1   | Unassigned 8-bit channel  |

| Channel 2   | Unassigned 8-bit channel  |

| Channel 3   | Unassigned 8-bit channel  |

| Channel 4   | Cascade channel           |

| Channel 5   | Unassigned 16-bit channel |

| Channel 6   | Unassigned 16-bit channel |

| Channel 7   | Unassigned 16-bit channel |

|             |                           |

Any advice or comments about our products and service, or anything we can help you with please don't hesitate to contact with us. We will do our best to support your products, projects and business.

Address: Global American, Inc.

17 Hampshire Drive Hudson, NH 03051

Telephone: Toll Free (U.S. Only) 800-833-8999

(603)886-3900

FAX: (603)886-4545

Website: <a href="http://www.globalamericaninc.com">http://www.globalamericaninc.com</a>

E-Mail: <a href="mailto:salesinfo@globalamericaninc.com">salesinfo@globalamericaninc.com</a>